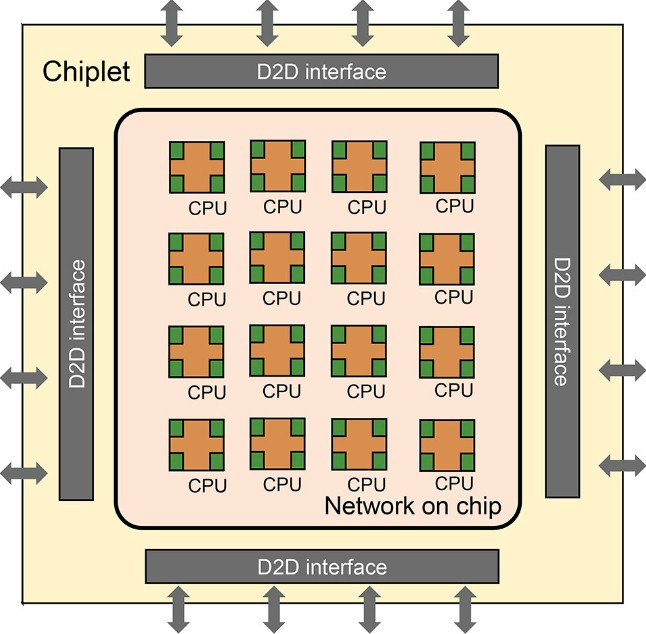

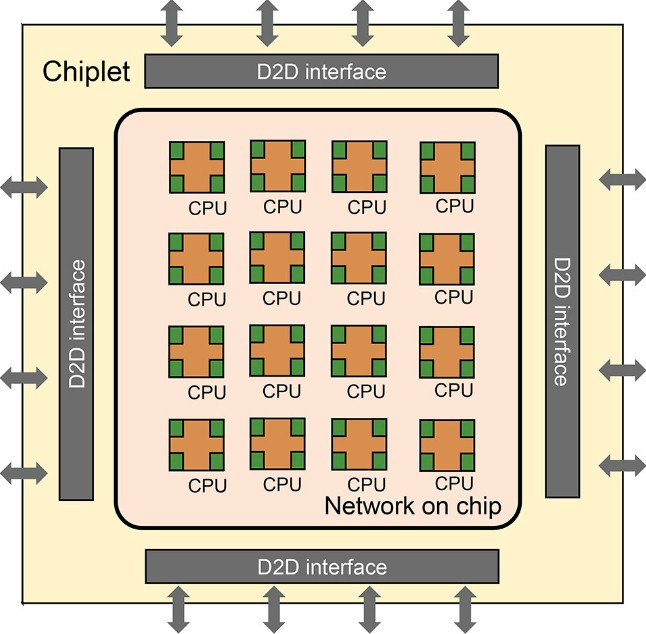

摩尔定律的终结对于芯片制造商来说正成为一大挑战。为了设计出容量更大的计算引擎(尽管速度可能不变),他们采用了两种策略:一是将设备分解成小的芯片(chiplets)并将其连接起来;二是在整块硅晶圆上进行蚀刻。这两种方法都可以与2.5D和3D堆叠技术相结合,为芯片带来更大的容量和功能。然而,无论采用哪种方法,都必须遵循用于蚀刻芯片的光刻设备的掩模版限制。目前的光刻设备是为300毫米硅晶圆定制的,其蚀刻面积为858平方毫米,这是不可改变的。过去三十年里,硅晶圆的尺寸从150毫米逐渐增加到200毫米再到300毫米,从可见光光刻到水浸光刻,再到极紫外光刻,也未改变这一限制。甚至考虑过450毫米的可能性,但掩模的限制仍然存在。实际上,450毫米晶圆的制造对于多家大型制造商如IBM、英特尔、三星、台积电等来说已经被认为是过于复杂,因此在2015年被放弃。这种限制不仅影响了小芯片的设计策略,还限制了在单个晶圆上的计算和内存块的大小。尽管450毫米的晶圆可能会带来某些惊人的效果,但目前的光刻技术并不支持一次性使用更大的掩模来蚀刻整个晶圆。因此,真正的挑战在于如何更有效地构建互连,以最大化计算和内存的潜在性。总体而言,尽管摩尔定律的终结带来了技术上的挑战,但行业仍然在寻求方法,既能构建更强大的计算引擎,又能降低制造成本。中国科学院计算技术研究所的研究团队在《Fundamental Research》期刊上发表了一篇论文,深入探讨了光刻技术和chiplets的极限问题。他们提出了一个被称为“大芯片”(Big Chip)的新型架构,该架构部分地借鉴了上世纪80年代Trilogy Systems的晶圆级系统设计,以及2020年代Cerebras Systems的架构。特斯拉也在开发其自主的“Dojo”超级计算机芯片,尽管它并非完全的晶圆级设计,但其复杂的Dojo D1核心布局有些许晶圆级设计的影子。然而,这篇论文虽然深入探讨了晶圆级设备的必要性,但对于他们所开发的“大芯片”架构的详细描述并不充分。我们并不清楚“大芯片”是否会采用与特斯拉Dojo相似的小芯片策略,还是直接是Cerebras那样的晶圆级设计。据介绍,名为“Zhejiang”的大芯片将使用22 nm工艺,预计由中芯国际 (SMIC) 制造,目前中芯国际不仅已经推出了14 nm工艺,而且正在试图通过 7 nm工艺提高产量。这款大芯片由 16 个小芯片组成,每个小芯片有 16 个 RISC-V 核心。论文显示,该设计能够在单一设备中扩展到100个芯片模块,这相当于一个包含1,600个核心的庞大系统。目前尚不清楚这 100 个小芯片将如何配置,也不清楚这些小芯片将实现什么样的内存架构。我们所知道的是,在当前的设计中,16个RISC-V处理器通过网络实现对称多处理,同时芯片模块之间也有链接,确保整个系统内存的共享和通信。以下是Zhejiang RISC-V 小芯片的框图:

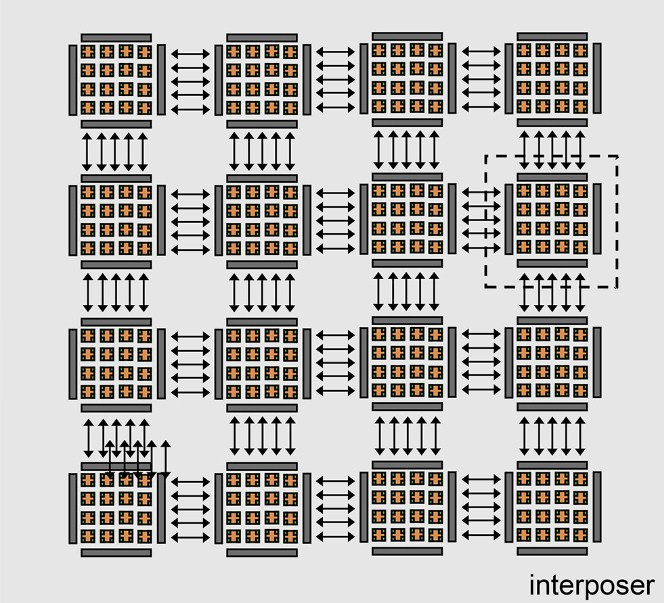

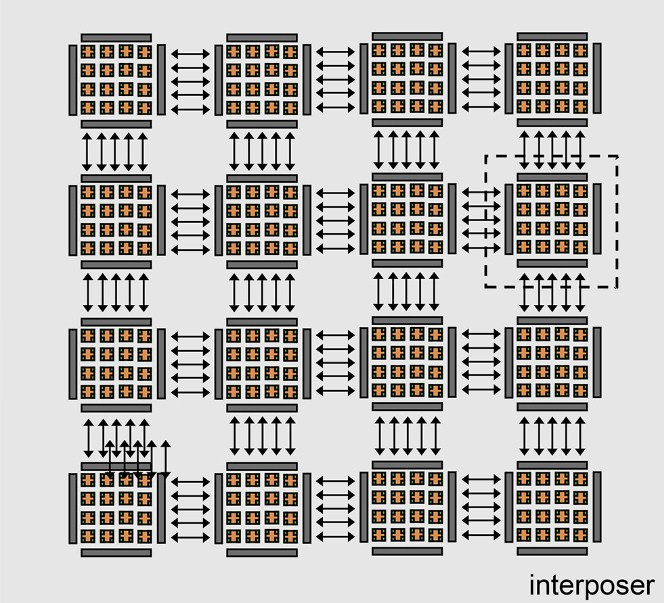

下图展示了如何使用中介层将 16 个小芯片捆绑在一起形成一个具有共享内存的 256 核计算复合体,从而实现芯片间 (D2D) 互连:

这种芯片模块设计完全可以作为晶圆级实现。不过当前迭代的版本看起来使用的是2.5D的中介层互连技术,这大概是目前中芯国际能够做到的最好的。

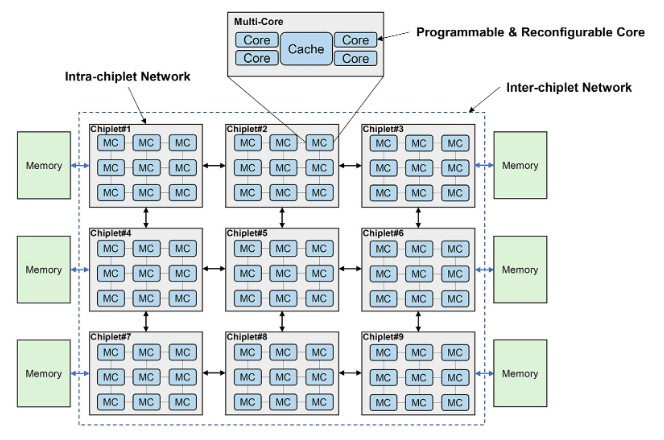

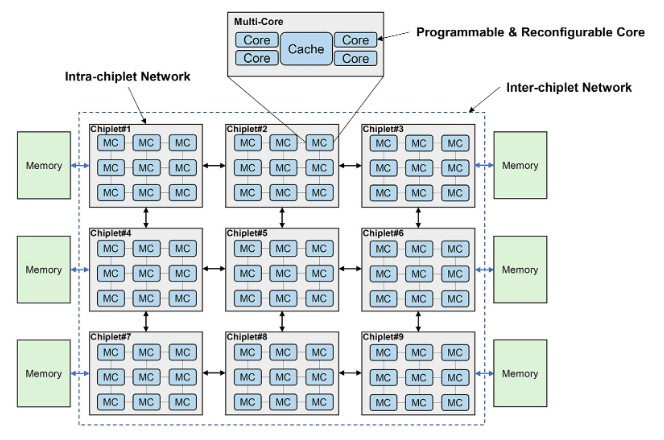

关于D2D互连的描述,研究人员提到:“我们使用了基于时间多路复用的通道共享技术进行接口设计。这种方法减少了芯片间的信号数量,从而降低了I/O接触点和中介层布线的资源需求,有效简化了基板设计。小芯片的I/O接触点位于顶部金属层。”尽管一个大芯片计算引擎作为多芯片模块或晶圆级系统非常吸引人,但关键在于如何连接这些设备以提供百亿亿级计算系统。“对于当前和未来的超大规模计算,我们预测分层小芯片架构将是一种强大而灵活的解决方案。分层小芯片架构被设计为多核多小芯片分层互连。在chiplet内部,核心之间采用超低延迟互连,而chiplet之间则采用低延迟互连,这得益于先进的封装技术,从而最大限度地降低了高可扩展性系统中的片上延迟和NUMA效应。在存储方面,系统采用了一个层次化的结构,包括核心内存、片上存储和片外存储。这三者在内存带宽、延迟、功耗和成本方面都有所不同。在分层chiplet架构中,多个核心通过交叉交换机连接并共享一个高速缓存。这形成了一个“pod”结构,pod通过chiplet内网络进行互连。多个pod再组成一个chiplet,chiplet通过chiplet间网络进行互连,然后连接到片外存储。为了最大化性能,需要精心设计和优化这种层次结构。合理利用内存带宽来平衡不同计算层次的工作负载,可以显著提高小芯片系统的整体效率。正确的通信网络设计也可以确保小芯片在处理共享内存任务时能够高效协同工作。”中科院研究人员表示。 图中的内核被描述为“可编程”和“可重新配置”,但这具体意味着什么还不确定。或许,这暗示了将采用诸如IBM的Power系列处理器中使用的可变线程技术,亦或是在核心中混合使用CPU和FPGA组件,目前一切都是未知数。论文显示,Big Chip计算引擎将由超过 1 万亿个晶体管组成,占据数千平方毫米的总面积,采用小芯片封装或晶圆级计算和存储块集成。考虑到高性能计算和人工智能应用的需求,中科院很可能正在探索 HBM 堆叠 DRAM 或类似英特尔和SK Hynix的MCR内存这样的双泵浦主内存技术。此外,RISV-V 内核可能会使用大量本地 SRAM 进行计算,这可能减少了对HBM内存的依赖,并允许使用 MCR 双泵浦技术加速 DDR5 内存。这很大程度上取决于具体的工作负载以及它们对内存容量和带宽的需求。Big Chip 的研究论文提出了一系列未来技术的愿景,例如光电计算、近内存计算以及3D 堆栈式缓存和主内存,不过中科院并未明确指出他们正在研究的具体方向和交付的时间表。

图中的内核被描述为“可编程”和“可重新配置”,但这具体意味着什么还不确定。或许,这暗示了将采用诸如IBM的Power系列处理器中使用的可变线程技术,亦或是在核心中混合使用CPU和FPGA组件,目前一切都是未知数。论文显示,Big Chip计算引擎将由超过 1 万亿个晶体管组成,占据数千平方毫米的总面积,采用小芯片封装或晶圆级计算和存储块集成。考虑到高性能计算和人工智能应用的需求,中科院很可能正在探索 HBM 堆叠 DRAM 或类似英特尔和SK Hynix的MCR内存这样的双泵浦主内存技术。此外,RISV-V 内核可能会使用大量本地 SRAM 进行计算,这可能减少了对HBM内存的依赖,并允许使用 MCR 双泵浦技术加速 DDR5 内存。这很大程度上取决于具体的工作负载以及它们对内存容量和带宽的需求。Big Chip 的研究论文提出了一系列未来技术的愿景,例如光电计算、近内存计算以及3D 堆栈式缓存和主内存,不过中科院并未明确指出他们正在研究的具体方向和交付的时间表。据了解,虽然中科院已经提出了Big Chip和相关系统的构想,但这些系统尚未实际构建。

图中的内核被描述为“可编程”和“可重新配置”,但这具体意味着什么还不确定。或许,这暗示了将采用诸如IBM的Power系列处理器中使用的可变线程技术,亦或是在核心中混合使用CPU和FPGA组件,目前一切都是未知数。

图中的内核被描述为“可编程”和“可重新配置”,但这具体意味着什么还不确定。或许,这暗示了将采用诸如IBM的Power系列处理器中使用的可变线程技术,亦或是在核心中混合使用CPU和FPGA组件,目前一切都是未知数。