在后摩尔时代,Chiplet已经成为芯片厂商进入下一创新阶段的桥梁,并为芯片设计突破PPA天花板提供了绝佳的技术选择。

3D封装正当时

而3D封装的优势还不限于此。相较于传统平面封装,3D封装通过缩短芯片之间的互连路径,提高了信号传输速度和可靠性。更短的互连路径减少了信号延迟和功耗,提高了整体电性能,并促进了更快的数据传输和处理速度。同时,3D封装支持多芯片和混合集成。它允许不同类型的芯片被集成到同一封装中,实现了高度灵活的系统设计。此外,3D封装有助于散热性能的改善。在紧密堆叠的情况下,热量的散发是一个挑战,但3D封装通过设计适当的散热通道和结构,提高了散热效率,保持芯片的稳定运行。

多个应用层面的动力共同推动了3D封装发展。

首先,高性能计算和处理需求对于3D封装提出了更高的要求,通过多芯片堆叠提供更高计算密度和处理能力。

其次,移动设备的小型化和功能增强推动了3D封装技术的应用,实现芯片堆叠和功能集成。

第三,物联网的发展需要集成多种功能模块,3D封装技术提供高度集成和紧凑设计的解决方案。

第四,高速通信和数据处理需求推动了短距离高密度互连的研究,提高信号传输和数据处理效率。同时,成本效益和制造技术的进步也推动了3D封装的发展,通过模块化设计和利用现有制造工艺降低成本。

研究机构Research and Markets的报告数据显示,2020年全球 3D半导体封装市场为 66亿美元,而到2026年修订后的规模将达到 147 亿美元,复合年增长率为14.6%。

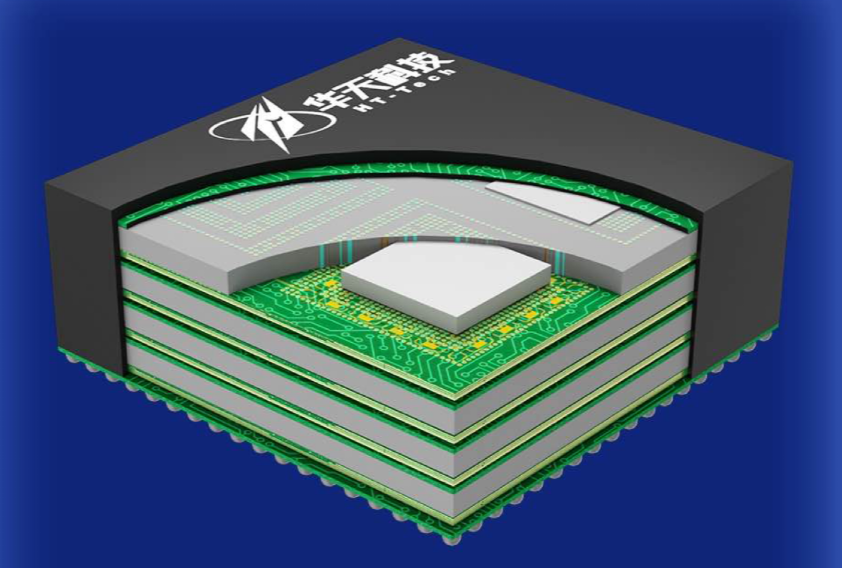

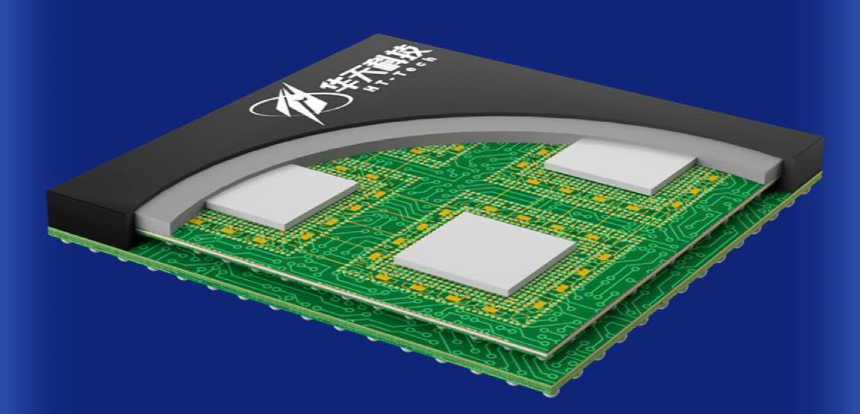

基于不同的技术路径,3D封装也呈现了多种形式,包括了引线键合多层芯片堆叠、封装堆叠(PoP)、3D扇出型封装等。各大半导体厂商也纷纷跟进,在3D封装技术上不断进行创新。比如,华天科技基于3D Matrix3D晶圆级封装平台开发的系统集成封装技术eSinc SiP,就通过集成硅基扇出封装,bumping技术, TSV技术,C2W和W2W技术,可以实现多芯片高密度高可靠性3D异质异构集成。

以硅基基板独步天下

eSinC(Embedded System in Chip)的全称是埋入集成系统级芯片技术,是华天科技2019年推出的3D封装技术。

eSiFO技术可将多颗芯片集成在一起,相比于传统封装整体封装尺寸大幅度缩减,芯片间互连更短,性能更强。在 eSiFO技术的基础上,华天科技继续开发了基于大空腔干法刻蚀、TSV盲孔和临时键合技术的3D扇出型晶圆级封装eSinC。该技术采用TSV通孔实现垂直方向互联,大大提高了互联密度和集成度。

esinC可实现的封装尺寸最大可以达到40mmx40mm,倒装芯片bump/pitch尺寸最小可以做到40um/70um,互联 TSV深宽比可以做到5:1,目前给客户出样的3D堆叠封装共集成8颗芯片,整体封装厚度小于1mm。该技术的目标应用主要是Al、loT、5G和处理器等众多领域。与市面上现有的3D晶圆级扇出封装技术(如lnFo-PoP)相比,eSinC技术通过高密度via last TSV实现3D互联。相较于 InFO-PoP的TMV技术,其互联密度更高,可以根据不同客户需求选择封装厚度,尤其在3D超薄高密度封装领域有独特的优势。

eSinC最大的优势还在于用硅基取代塑封料。以硅基作为载体,其热膨胀系数、杨氏模量及热导率均优于塑封料,且硅载体与芯片材质相同,因此eSinC的晶圆翘曲会明显小于InFo-PoP,且eSinC产品的散热性能要明显好于InFo-PoP产品;同时,由于使用了硅基作为载体,兼容成熟的硅工艺,可以通过TSV工艺实现高密度3D互联,并通过硅刻蚀工艺制备出用于嵌入芯片的硅基凹槽结构,从而实现芯片的3D集成。

在eSinC晶圆上贴装芯片或两个eSinc晶圆进行堆叠,就成为了3D FO SiP封装技术,可以实现不同结构的SiP封装。而该技术与TSV和eSiFo一起,还构成了华天科技的3D Matrix晶圆封装平台。

为国内CHIPLET发展增动力

Chiplet的快速发展必然对封装技术提出更高的要求。当单个硅片被分割成多个芯粒,再把这些芯粒封装在一起,由于单颗硅片上的布线密度和信号传输质量远高于不同芯粒,这就要求必须要发展出高密度、大带宽布线的先进封装技术,尽可能提升在多个Chiplet之间布线的数量并提升信号传输质量。

当前,Chiplet所采用的先进封装主要有以下三种形式:一是在有机基板上直接进行系统集成, 二是在有机基板上嵌入硅桥后进行集成,三是采用2.5D封装工艺,如台积电的CoWoS工艺。这三种封装形式都需要有机基板,因为高端基板的产能欠缺,给封装厂造成了很大的挑战,也形成了很高的技术门槛。

eSinC工艺的优势在此完全体现。由于不需要有机基板,eSinC克服了上述三种封装形式门槛高的问题,因此成为封装厂实现Chiplet封装的重要方案,更有利于整个技术的推广。

为了适应Chiplet技术发展的节奏,华天科技还为eSinC技术规划了三个发展目标。首先,随着集成的芯片数量不断增多,单颗芯片的尺寸也越来越大,封装尺寸会逐渐增大;第二,TSV深宽比越来越大,pitch尺寸减小;第三,RDL线宽线距越来越小,层数会越来越多,以应对芯片功能强大以后1/0密度不断增加的趋势。

Chiplet在国内刚刚起步,业界很多用于Chiplet的3D封装技术都是以台积电的3D fabric为蓝本进行技术创新。但是,华天科技推出的eSinC技术属于独立自主开发的Chiplet封装技术,无论是对公司打开Chiplet高端封装技术领域,还是对国内发展Chiplet产业都具有重大意义。未来,在此技术基础上进一步结合fine pitch RDL、hybrid bond、高级基板等平台技术,可以进一步提升封装密度,建立完整的Chiplet封装平台。

发展独立的封装技术,对国内整个Chiplet封装产业链也有很大的拉动作用,特别是国产化装备和国产化材料将会迎来新的发展机遇。当前,先进封装所需的关键设备,如刻蚀机、PVD等和部分材料已实现了国产化,但还有一些后端设备和关键材料需要攻关,而以eSinc技术为引领,将会加快这些环节的国产化进度。同时,eSinC也会引领先进封装的技术突破,如Fine pitch RDL,Interposer、混合键合、大颗FCBGA技术等

在全球科技竞争日益激烈的大环境和国内半导体关键技术面临封锁的背景下,要发展我们独立自主的Chiplet技术,要在技术上实现创新,以eSinc这样的独创技术为引导,进一步推动先进封装关键设备、关键材料的国产化,改变关键设备、关键材料依赖进口的被动局面,早日实现供应链的自主可控。