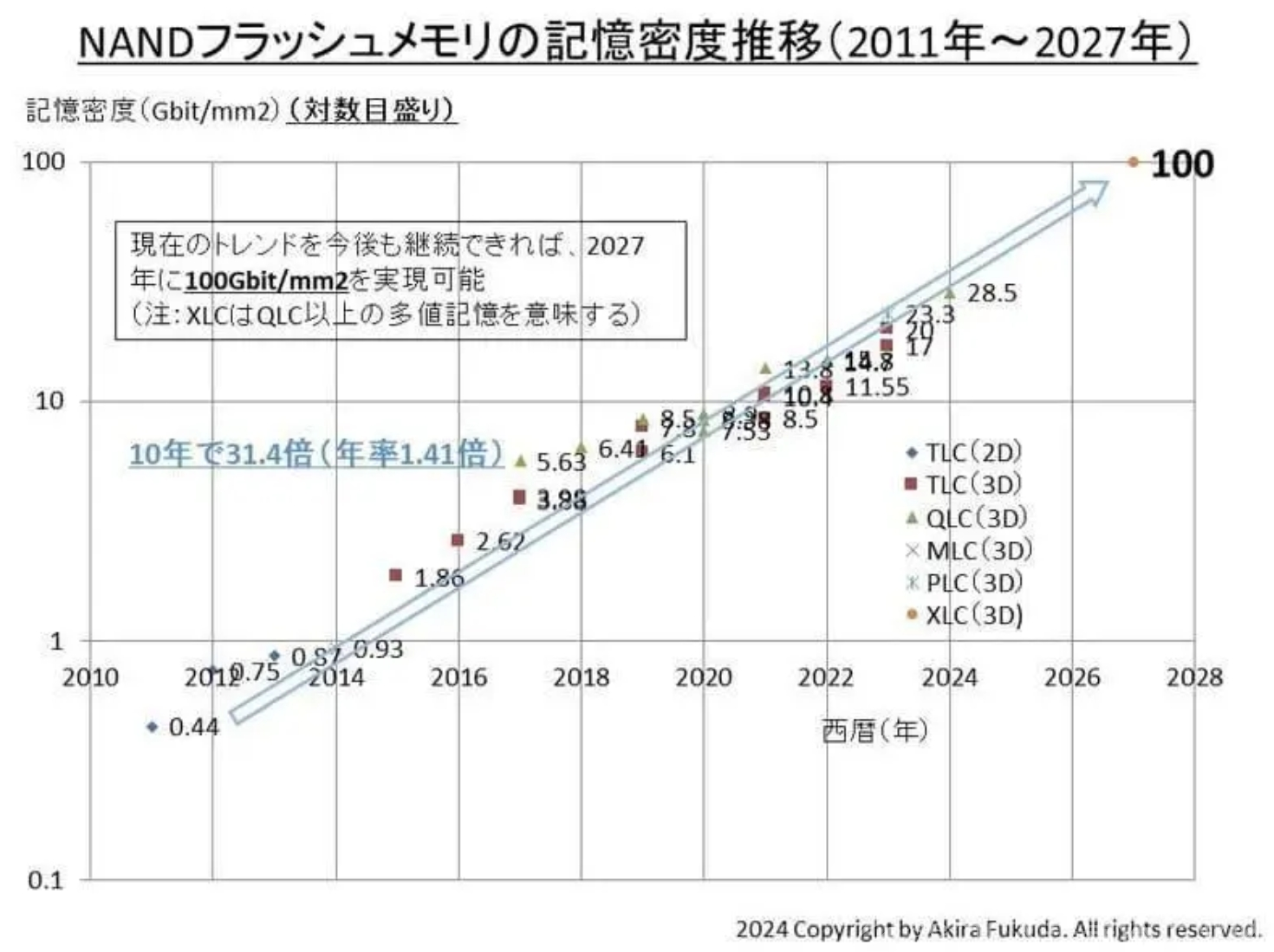

据外媒报道,近期,铠侠(Kioxia)公布了其3D NAND闪存技术路线图,目标在2027年实现1000层堆叠。

3D NAND层数普遍从2014年的24层增加到2022年的238层,八年间增长了10倍。铠侠表示,以每年1.33倍的增长率,到2027年将可达到1,000层的水平。

然而,层数越多意味着蚀刻垂直连接孔(硅通孔或 TSV)就越困难,因为 TSV 尺寸可能会扭曲,通道材料层也会变形。更深的通孔会导致更高的沟道电阻,堆叠层内的电气连接也会受到损害,因为电流的传输路径更长,从而导致电阻影响电流。铠侠正在考虑将字线材料从钨改为钼,以降低电流电阻和相关的延迟时间。

报道称,铠侠在去年推出了BiCS8 3D NAND闪存,为218层。利用了1Tb三层单元(TLC)和四层单元(QLC)的四个平面,通过创新的横向收缩技术,将位密度提高了50%以上。若铠侠想在2027年实现1000层堆叠,可能需要过渡到五层单元(PLC)。

值得一提的是,三星曾在上个月表示,计划2030年之前推出超过1000层的先进NAND闪存芯片,还将引入新型铁电材料应用于NAND闪存芯片的制造上,以实现这一目标。