未来半导体12月20日综合报告,在12月16日举办的“第二届中国互连技术与产业大会”上,首个由中国集成电路领域相关企业和专家共同主导制定的《小芯片接口总线技术要求》团体标准正式通过工信部中国电子工业标准化技术协会的审定并发布。

据悉,这是中国首个原生Chiplet技术标准,旨在为中国半导体厂商在chiplet领域的发展制定相对统一的标准,提高来自不同制造商的小芯片之间的互操作性。

此次标准的发布,对封装产业的带动也不言而喻。封测是半导体产业链中的后道工序,在传统的认知中,封测环节似乎仅仅是个“加工商”,但随着chiplet技术的发展,封测厂商走向舞台中央,担任起“解决方案提供商”的角色。

今年 3 月 28 日,由中国计算机互连技术联盟(CCITA)联合电子标准院,多家企业、科研院所等经过 10 个月努力共同制订的《小芯片接口总线技术要求》、《微电子芯片光互连接口技术》完成标准草案制定,开始面向社会征求意见。

《小芯片接口总线技术要求》描述了 CPU、GPU、人工智能芯片、网络处理器和网络交换芯片等应用场景的小芯片接口总线(chip-let)技术要求,包括总体概述、接口要求、链路层、适配层、物理层和封装要求等。

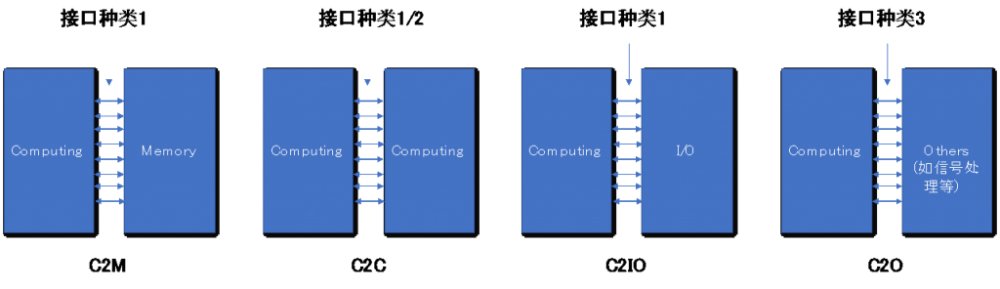

据介绍,小芯片接口技术有以下应用场景:C2M (Computing to Memory),计算芯片与存储芯片的互连。C2C (Computing to Computing),计算芯片之间的互连。两者连接方式:采用并行单端信号相连,多用于 CPU 内多计算芯片之间的互连。采用串行差分信号相连,多用于 AI、Switch 芯片性能扩展的场景。C2IO (Computing to IO),计算芯片与 IO 芯片的互连。C2O (Computing to Others),计算芯片与信号处理、基带单元等其他小芯片的互连。

此标准列出了并行总线等三种接口,提出了多种速率要求,总连接带宽可以达到 1.6Tbps,以灵活应对不同的应用场景以及不同能力的技术供应商,通过对链路层、适配层、物理层的详细定义,实现在小芯片之间的互连互通,并兼顾了 PCIe 等现有协议的支持,列出了对封装方式的要求,小芯片设计不但可以使用国际先进封装方式,也可以充分利用国内封装技术积累。

作为突破摩尔定律限制的重要技术思路,Chiplet可以有效的平衡芯片效能、成本以及良率之间的关系,一度成为半导体厂商们竞逐的方向。不过,Chiplet要实现更大范围内的应用,就需要混合来自多家芯片厂商或多个工艺节点的裸片,可能会涉及到多家各种功能芯片的设计、互连、接口。正是由于缺少统一的标准,chiplet发展阻碍重重。

今年3月,国际上正式成立了UCIe(Universal Chiplet Interconnect Express)产业联盟由日月光、AMD、ARM、Google Cloud、Intel、微软、高通、三星和台积电十家公司正式成立,联盟成员将携手推动Chiplet接口规范的标准化,并已推出UCIe 1.0版本规范。UCIe是一种开放的Chiplet互连规范,其定义了封装内Chiplet之间的互连,以实现Chiplet在封装级别的普遍互连和开放的Chiplet生态系统。

生态建设是一项技术革命的关键,唯有产业链中越来越多厂商开始采用Chiplet设计的时候,才能使国内整个Chiplet生态更成熟稳定。令人欣喜的是,目前多家半导体头部厂商都已加快在Chiplet领域的布局。根据研究机构Omdia预测,到2024年,Chiplet的市场规模将达到58亿美元,2035年则超过570亿美元,Chiplet的全球市场规模将迎来快速增长。