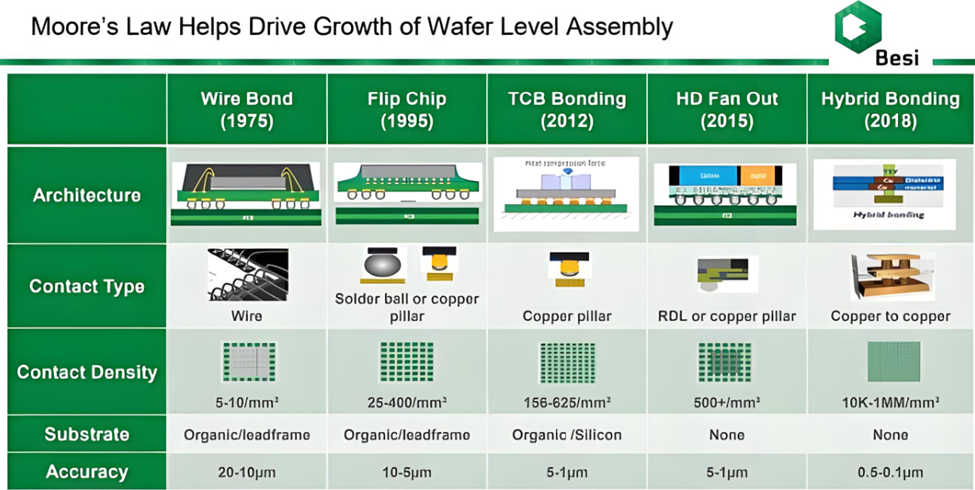

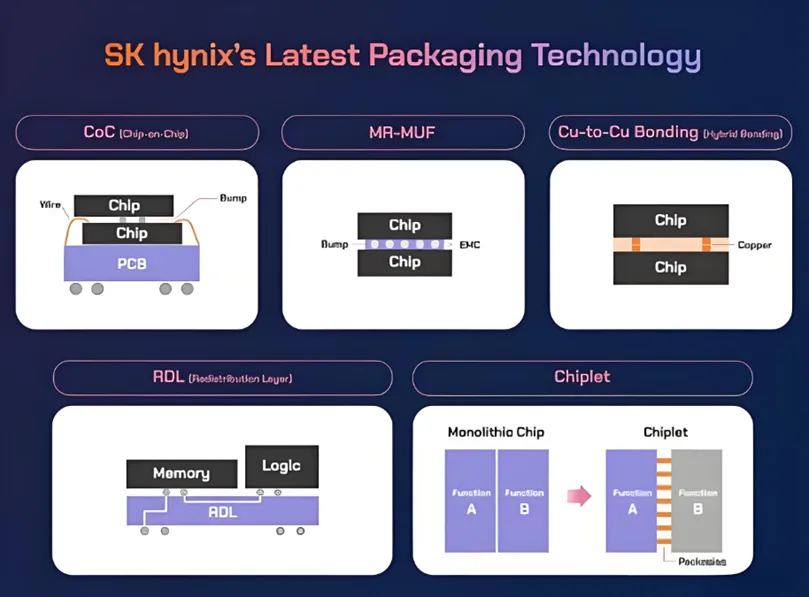

目前,晶体管的尺寸日益逼近物理极限,半导体巨头们开始依赖先进封装技术以延续摩尔定律并推动芯片性能的提升。“混合键合”(Hybrid Bonding)因其能大幅缩小芯片连接间距、做出更多I/O接口,降低芯片堆栈厚度从而支持更高的数据传输速度并实现更低的能耗,而被视为先进封装领域的重点发展技术。

混合键合将是封装技术发展的重点(来源:Besi)

什么是混合键合?

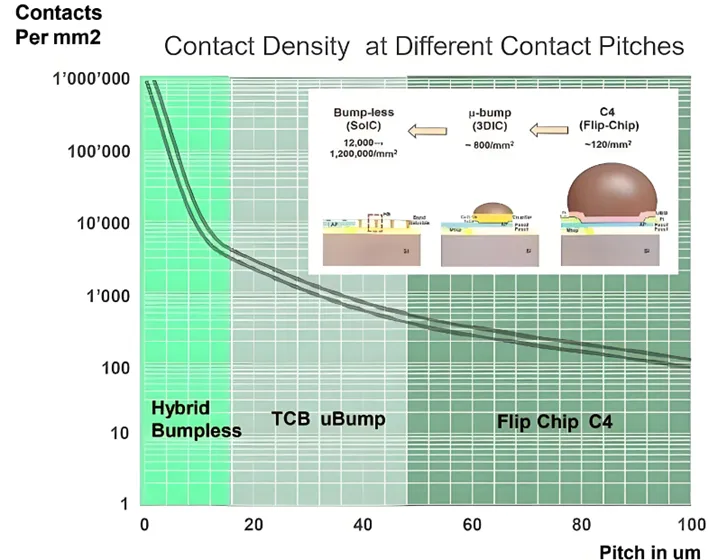

混合键合是在异质或同质芯片之间创建永久键合的过程,可用于实现不同芯片之间的高密度、高性能互联。其中“混合”是指在两个表面之间形成电介质-电介质和金属-金属键。通过紧密嵌入电介质中的微小铜焊盘直接键合,可提供比传统的铜微凸块互连的方式多 1,000 倍的 I/O 连接,为10 μm及以下的间距提供了解决方案,并将信号延迟驱动至接近零水平,从而能够在极小的空间内实现超精细间距的堆叠和封装,达到三维集成的目的。混合键合支持各种可能的芯片架构,主要针对高端应用,包括高性能计算、人工智能、服务器和数据中心等。

10µm以下间距是Hybrid Bonding的主战场。(来源:Besi)

高端CPU已经采用混合键合技术

AMD 3D 芯片技术 (来源:AMD)

AMD V-Cache 采用的台积电的3DFabric封装-SoIC就采用了混合键和TSV,SoIC技术为芯片I/O提供了强大的键合间距可扩展性,从而实现了高密度芯片间互连。相较微凸块(μbumps),让芯片接点密度提升15倍,互联能效超过三倍。打造高性能游戏处理器。

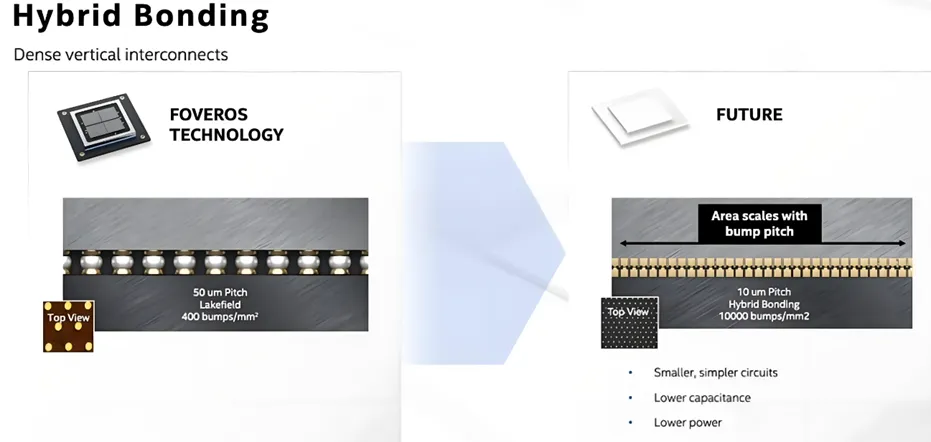

英特尔2020年公布Hybrid Bonding进度,芯片间距可缩小至10µm(来源:英特尔)

英特尔的3D封装Foveros Direct亦采用晶粒对晶圆(Die to Wafer)的混合键合技术,大幅缩小芯片间距。

SK海力士的先进封装发展中,同样包含混合键合,它的16层DRAM HBM4产品也可能采用此技术(来源:SK海力士)

Evatec 的解决方案

针对日益精进的混合键合技术需求,Evatec 可以提供三类解决方案,包括Bumping(凸块)、TSV seed layer(硅通孔晶种层)以及采用PVD沉积方式的介电层SiN/SiCN的半导体膜层沉积。

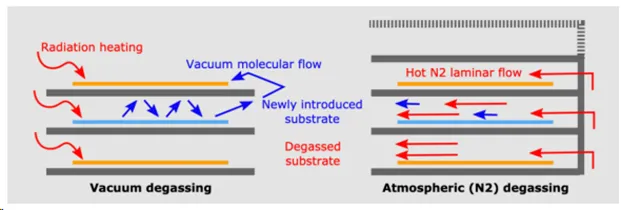

Bumping

Evatec 创新地采用了ABD(Atmosphere Batch Degas, 即大气批次式脱气)的方式进行前处理。其优点包括对于晶圆精确的温度控制(利用传导加热,BKM120℃±10℃),独立于辐射率的温度控制(无局部冷点或热点)以及通过惰性气体(N2)层流对晶圆有机挥发物的有效排出(无再污染)。

真空除水气 vs. 大气除水气

接下来的Pre-Clean 工艺,我们采用ICP(电感耦合等离子体)在300mm 晶圆上实现了均匀性<3%(1σ, EE 5mm),达到了晶圆级封装工艺的规格。

300 毫米晶圆上的蚀刻均匀性

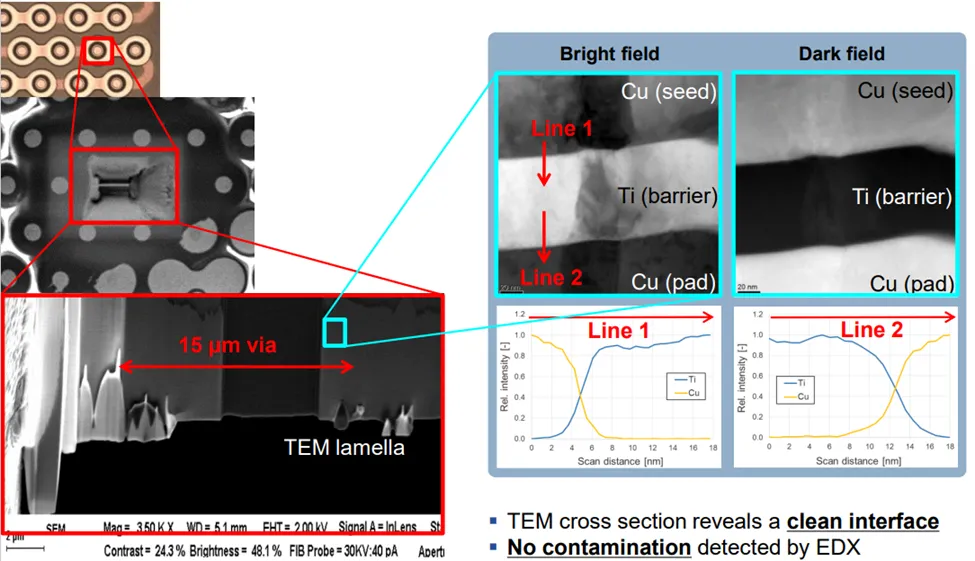

另外我们通过TEM 分析发现铜垫和晶种层界面未发现污染或氧化现象,这表明我们的解决方案提供了最佳的接触电阻 (Rc) 和晶种层附着力。

Cu-Pad 和晶界的 TEM元素分析

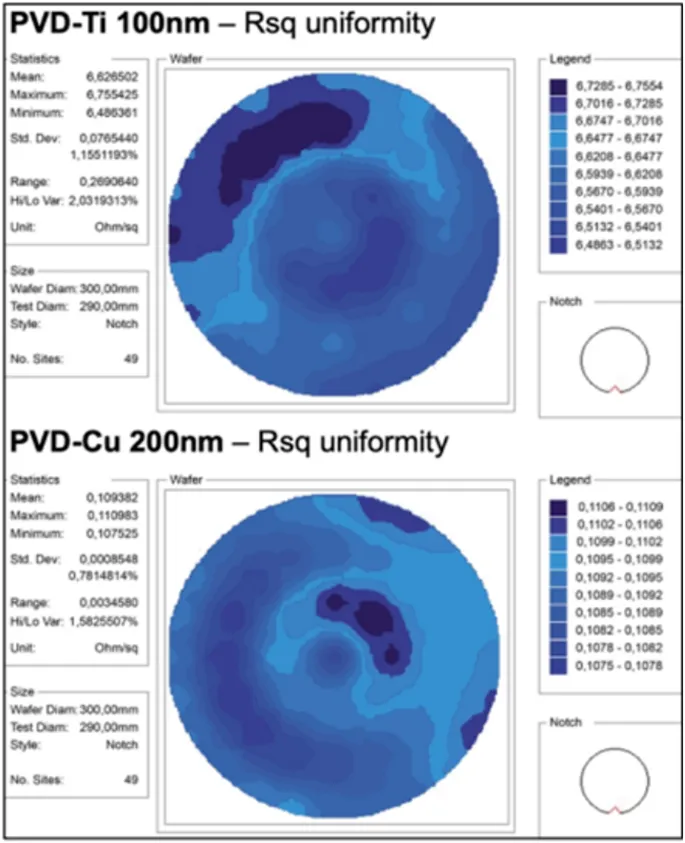

下图展示了所需的钛层和铜层的在300mm 晶圆沉积均匀性的结果。

300mm 晶圆上的沉积均匀度结果

Hexagon®

CLUSTERLINE® 300

如果您还想进一步了解 Evatec 的 Bumping 沉积技术,可以查看本公众号的往期文章 基于高有机材质负载基板的超低接触电阻(Rc)晶种层沉积技术