作者:

Coventor(泛林集团旗下公司)半导体工艺与整合(SPI)高级工程师王青鹏博士

实验设计(DOE)是半导体工程研发中一个强大的概念,它是研究实验变量敏感性及其对器件性能影响的利器。如果DOE经过精心设计,工程师就可以使用有限的实验晶圆及试验成本实现半导体器件的目标性能。然而,在半导体设计和制造领域,DOE(或实验)空间通常并未得到充分探索。相反,人们经常使用非常传统的试错方案来挖掘有限的实验空间。这是因为在半导体制造工艺中存在着太多变量,如果要充分探索所有变量的可能情况,需要极大的晶圆数量和试验成本。在这种情况下,虚拟工艺模型和虚拟DOE可谓是探索巨大潜在解空间、加速工艺发展的同时减少硅实验成本的重要工具。本文将说明我们在高深宽比通孔钨填充工艺中,利用虚拟DOE实现了对空隙的有效控制和消除。示例中,我们使用原位沉积-刻蚀-沉积 (DED) 法进行钨填充工艺。

基于硅的扫描电镜图像和每个填充步骤的基本行为,使用SEMulator3D®虚拟工艺建模,重建了通孔钨填充工艺。

建模工艺包括:

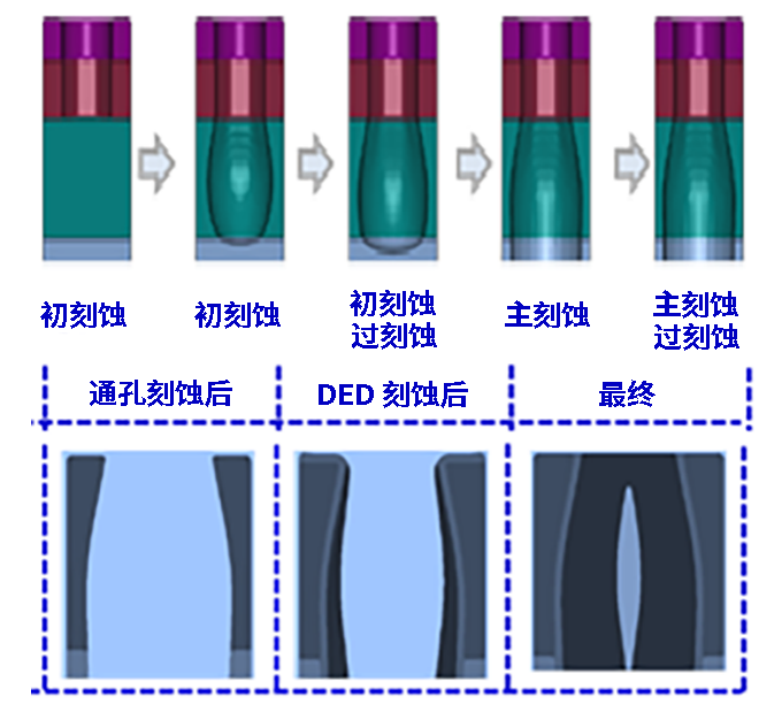

1. 前置沟槽刻蚀(初刻蚀、初刻蚀过刻蚀、主刻蚀、过刻蚀)

2. DED工艺(第一次沉积、第一次深度相关刻蚀、第二次沉积工艺)

3. 空隙定位和空隙体积的虚拟测量

为了匹配实际的硅剖面,工艺模型中的每个步骤都经过校准。

使用SEMulator3D生成的模拟3D输出结构与硅的图像进行对比,它们具有相似的空隙位置和空隙体积(见图1)。图1显示了SEMulator3D和实际硅晶圆中的相应工艺步骤。使用新校准的模型,完成了3次虚拟DOE和500多次模拟运行,以了解不同工艺变量对空隙体积和弯曲关键尺寸的影响。

图1:DED工艺校准

图1:DED工艺校准

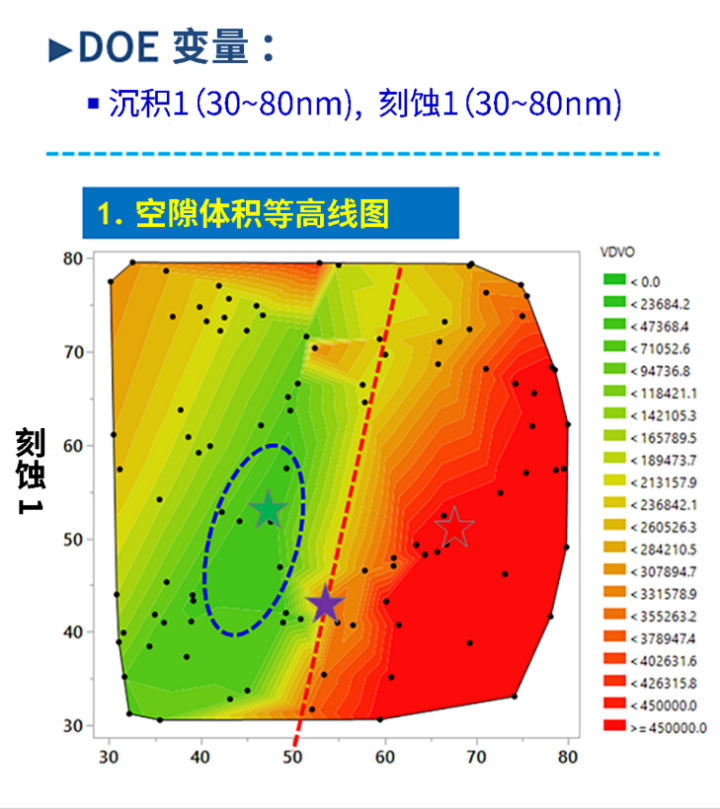

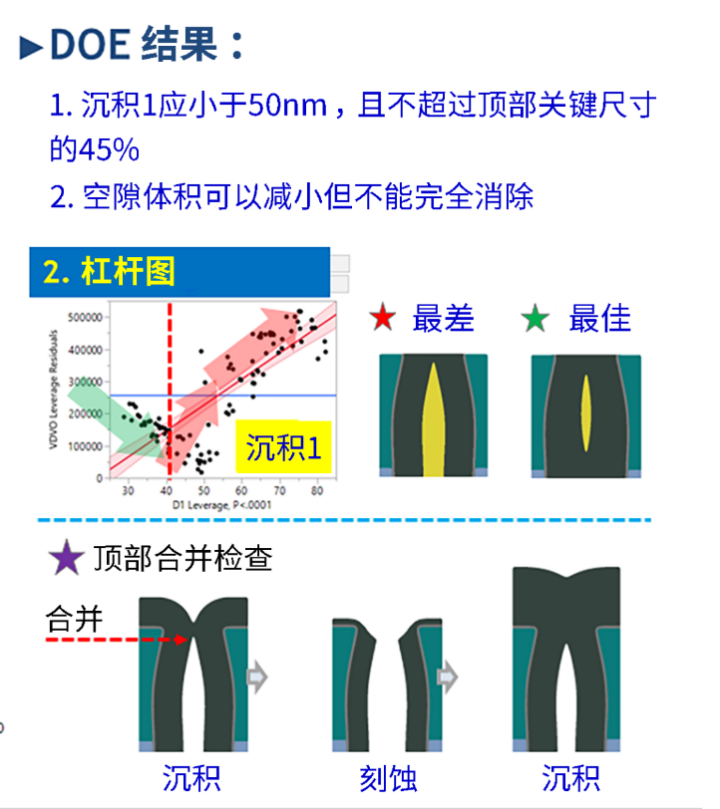

l第一次DOE

在第一次DOE中,我们使用DED工艺步骤进行了沉积和刻蚀量的实验。在我们的测试条件下,空隙体积可以减小但永远不能化零,并且沉积层不应超过顶部关键尺寸的45%(见图 2)。

图2:DED等高线图、杠杆图、DOE1的输出结构

●第二次DOE

在第二次DOE中,我们给校准模型(DEDED工艺流程的顺序)加入了新的沉积/刻蚀工艺步骤。这些新的沉积和刻蚀步骤被设置了与第一次 DOE相同的沉积和刻蚀范围(沉积1和刻蚀1)。沉积1(D1)/刻蚀1(E1)实验表明,在D1和E1值分别为47nm和52nm时可以获得无空隙结构(见图 3)。需要注意,与第一次DOE相比,DEDED工艺流程中加入了新的沉积和刻蚀步骤。与之前使用的简单DED工艺相比,这意味着工艺时间的增加和生产量的降低。

图3:DEDED等高线图、杠杆图、DOE2的输出结构

●第三次DOE

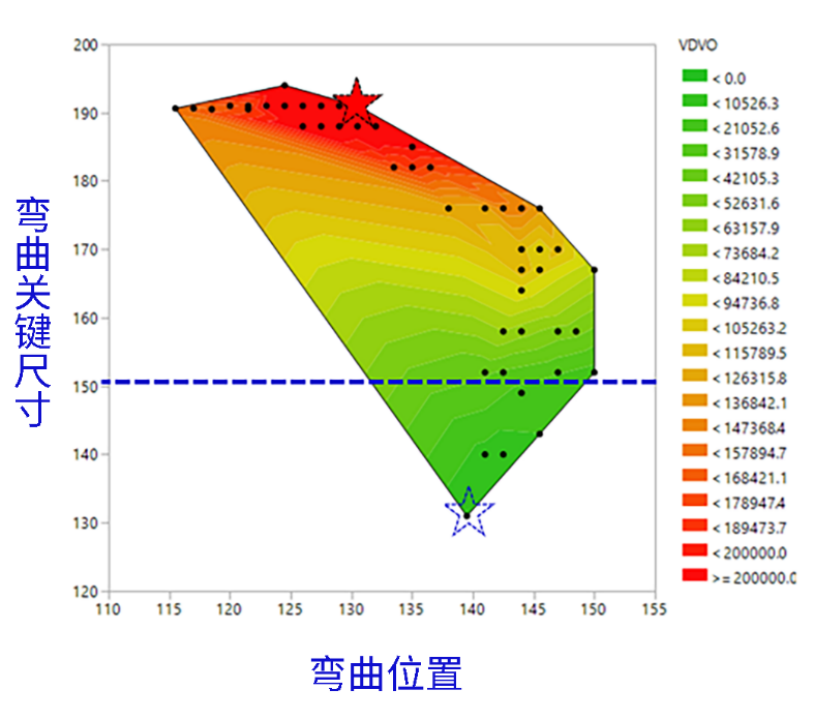

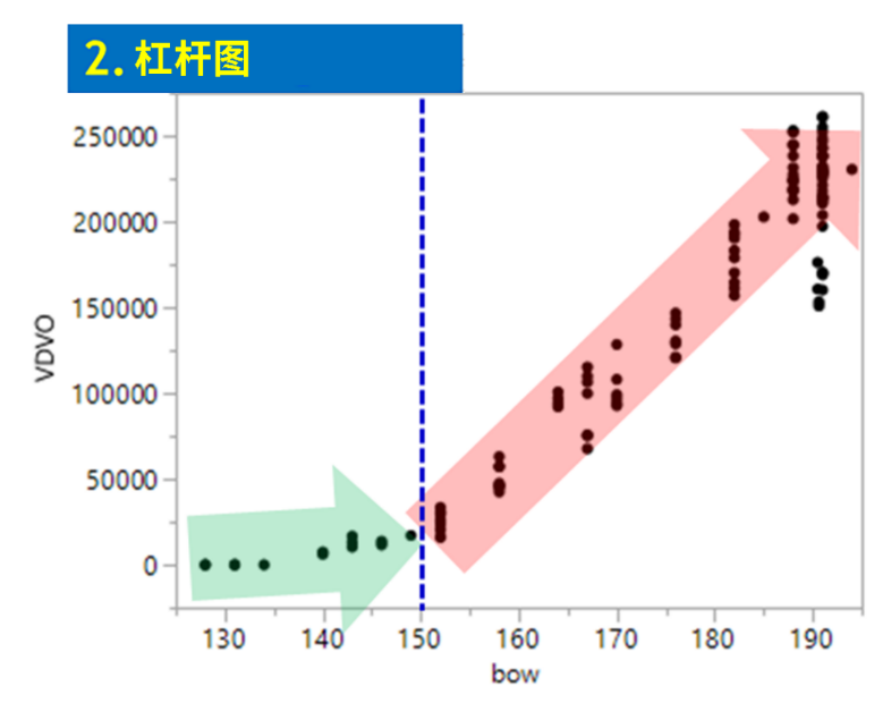

在第三次DOE中,我们通过调整BT(初刻蚀)刻蚀行为参数进行了一项前置通孔剖面的实验。在BT刻蚀实验中,使用SEMulator3D的可视性刻蚀功能进行了工艺建模。我们在虚拟实验中修改的是等离子体入射角度分布(BTA)和过刻蚀因子(Fact)这两个输入参数。完成虚拟通孔刻蚀后,使用虚拟测量来估测每次模拟运行的最大弯曲关键尺寸和位置。这个方法使用BTA(初刻蚀等离子体入射角度分布)和Fact(过刻蚀量)实验实验生成了虚拟结构,同时测量和绘制了弯曲关键尺寸和位置。第三次DOE的结果表明,当弯曲关键尺寸足够小时,可以获得无空隙的结构;当弯曲关键尺寸大于150nm时,空隙体积将急剧增加(见图4)。 因此,可以利用最佳的第三次DOE结果来选择我们的制造参数并进行硅验证。

图4:前置通孔剖面实验等高线图、杠杆图、DOE3的输出结构

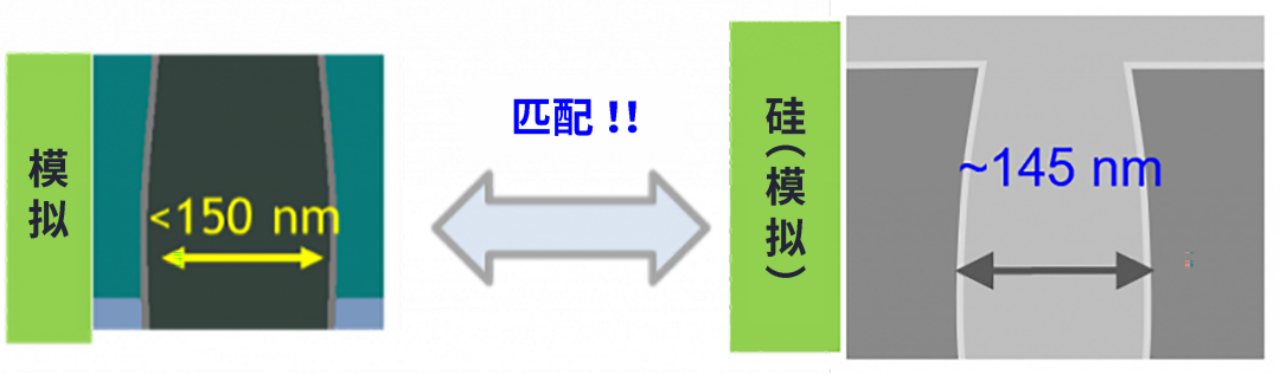

通过将前置通孔弯曲规格设置在150nm以下(图5中的145nm),我们在最终的硅工艺中获得了无空隙结构。此次,硅结果与模型预测相符,空隙问题得到解决。

图5:当弯曲关键尺寸小于150nm时,SEMulator3D预测的结果与实际的硅结果

此次演示中,我们进行了SEMulator3D建模和虚拟DOE来优化DED钨填充,并生成无空隙结构,3次DOE都得到了空隙减小或无空隙的结构。我们用DOE3的结果进行了硅验证,并证明我们解决了空隙问题。硅结果与模型预测相匹配,且所用时间比试错验证可能会花费的短很多。该实验表明,虚拟DOE在加速工艺发展并降低硅晶圆测试成本的同时,也能成功降低DED钨填充工艺中的空隙体积。